RISC-V

RISC-V (“risc-five”) is an open Instruction Set Architecture (ISA) based on the well known RISC principles. If you’re interested in its history and design innovations please refer to the dedicated Wikipedia page.

RISC-emV

RISC-emV is how me and Davide named our project for the Advanced Computing Architectures course at University of Trento. The name comes from what the software is: a RISC-V emulator. Everything is hosted on my Github at AlexSartori/RISC-emV, where you will also find a more technical documentation of the code.

Features

We wrote it in Python 3.x & PyQt5, and it currently provides the following features:

- Emulation of the Tomasulo Algorithm

- Support for Simultaneous Multithreading

- ELF-file/object-code disassembling

- Step-by-step or continuous execution with variable delay

- Configurable ISA: customize every instruction’s running-time in cycles and its equivalent pseudocode

- Expandable ISA: current support is for RV32I, RV32M and RV32F, but you can contribute and add any ISA extension just by editing a JSON file

- Configurable environment (Data Memory size, number of Reservation Stations/Functional Units, …)

- Ready-to-use sample programs

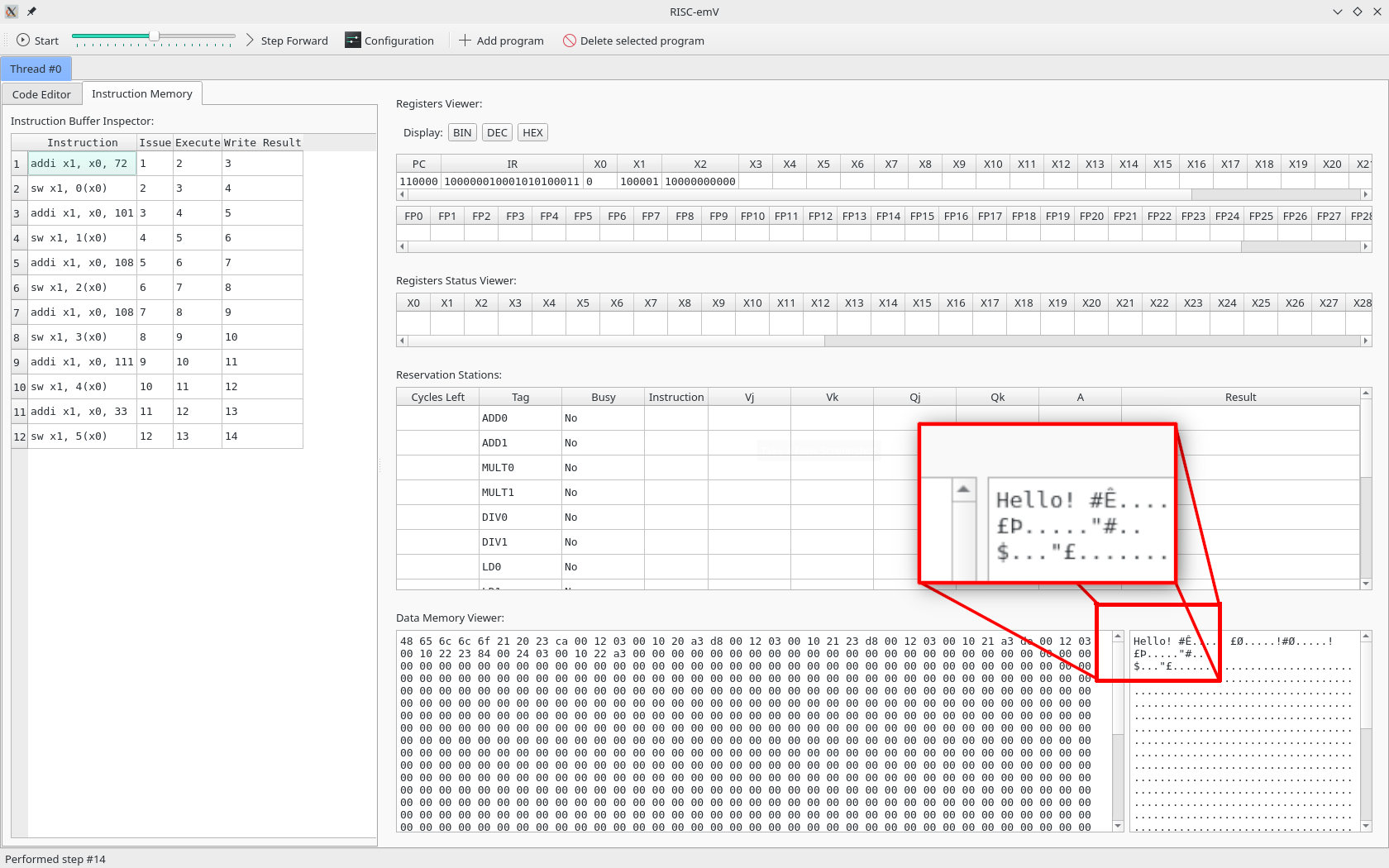

Graphical Interface

The GUI is mainly composed of two vertical panels: the one on the left lets the user interact with the code being executed, while the rightmost one displays the state of the emulator components. The code panel has two tabs, one with a text editor which allows for both writing code and for loading/disassembling external programs, and another tab (displayed in the picture above) showing the contents of the instruction memory and some details about active instructions such as issue time, execution length and finish time. On the right panel, the displayed components are, in order from top to bottom: integer registers, FP registers, register status table, reservation stations/functional units, and data memory dump.

Installation and Usage

Until made available on the official PyPI repositories, the software is installable by cloning the Github repository and installing it locally:

$ git clone https://github.com/AlexSartori/RISC-emV

$ cd RISC-emV

$ pip install -e .

Then simply launch it with:

$ riscemv

At this point the GUI will pop up. You can either write your own code or import an existing program with “Open” button. Next, click “Load” to parse the instructions and load them into memory. If you haven’t provided a .text section or an entry point, RISC-emV will do it for you now.

At this point, the only thing left to do is to start the execution: you can either request the emulator to perform a single step with the “Step Forward” button, or start a continuous execution with the “Start” button, which will interleave a delay between every instruction proportional to the value of the slider on the top bar. Lastly, a double-click on any field of a component will allow you to edit the associated value, be it a register or a functional unit.

If you have any suggestion don’t hesitate to reach out, file an issue on Github, or even create a pull request with any improvement!